Polymers | Free Full-Text | Interfacial Phenomena in Multi-Micro-/Nanolayered Polymer Coextrusion: A Review of Fundamental and Engineering Aspects

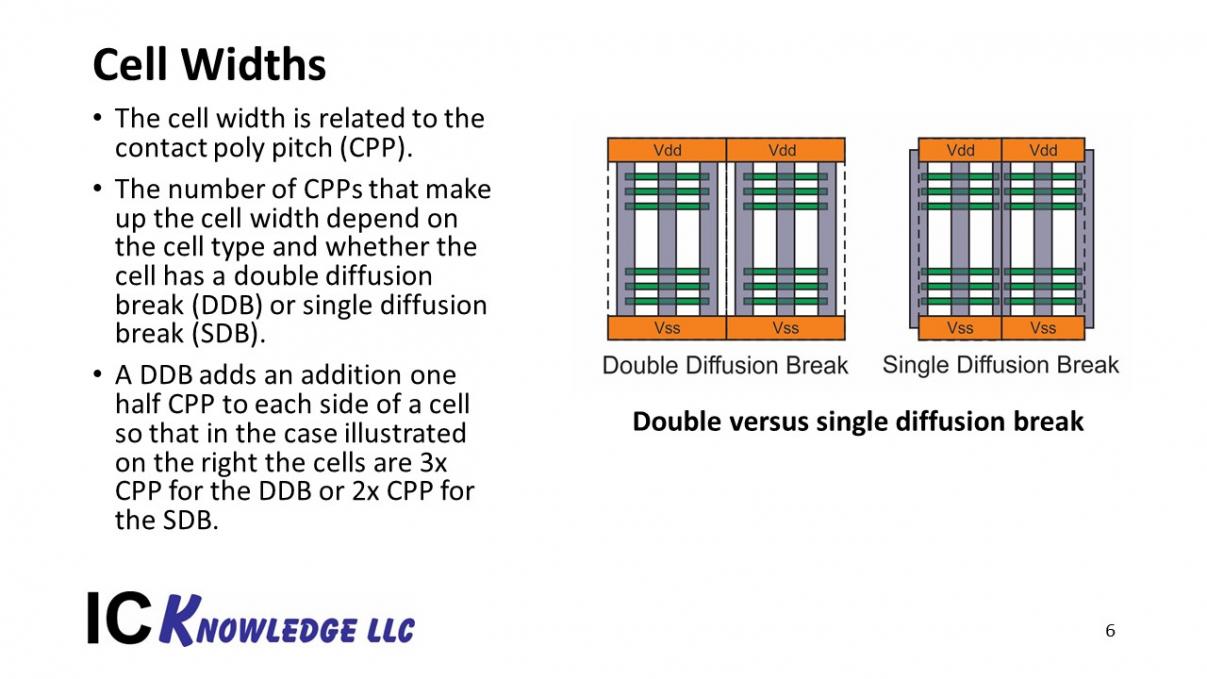

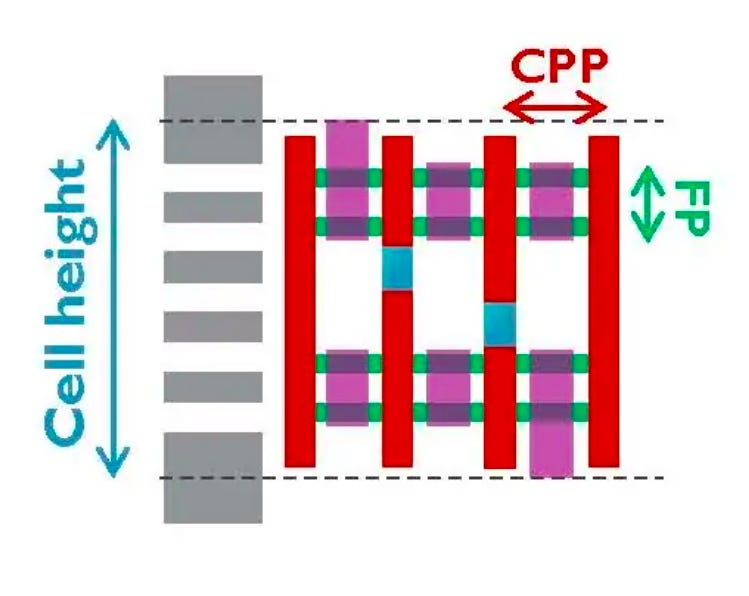

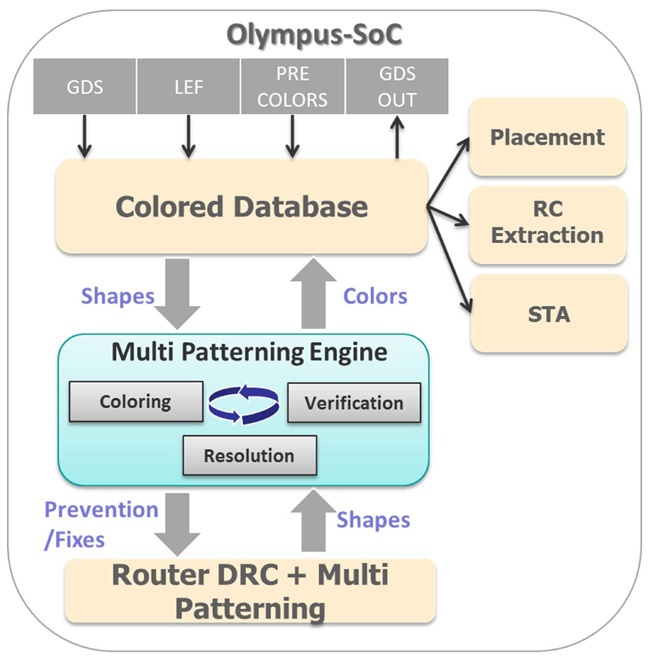

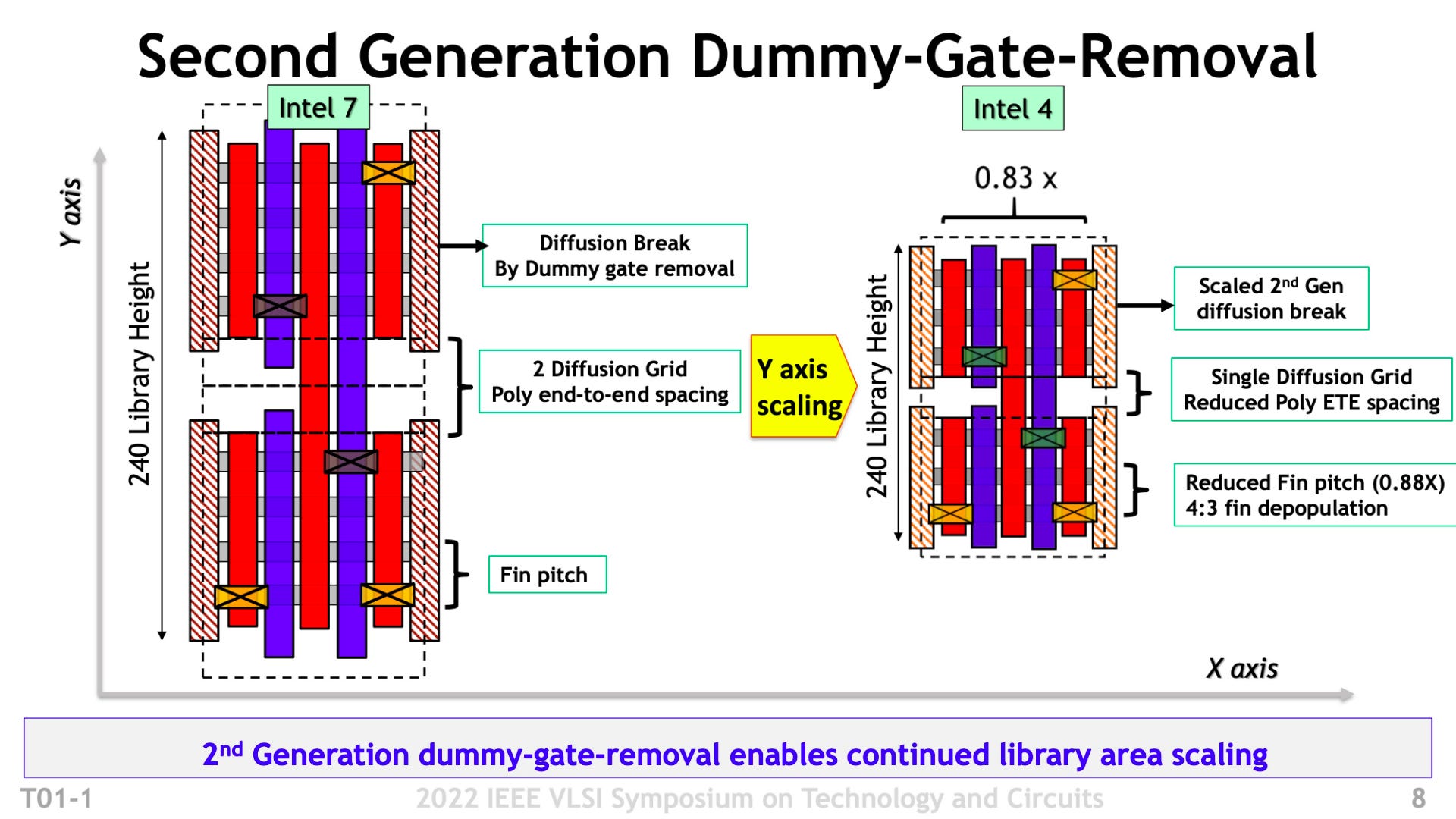

Chip Variability Mitigation through Continuous Diffusion Enabled by EUV and Self-Aligned Gate Contact | Semantic Scholar

Ultrafast Internal Exciton Dissociation through Edge States in MoS2 Nanosheets with Diffusion Blocking | Nano Letters

Rapid Online Analysis of Photopolymerization Kinetics and Molecular Weight Using Diffusion NMR | ACS Macro Letters

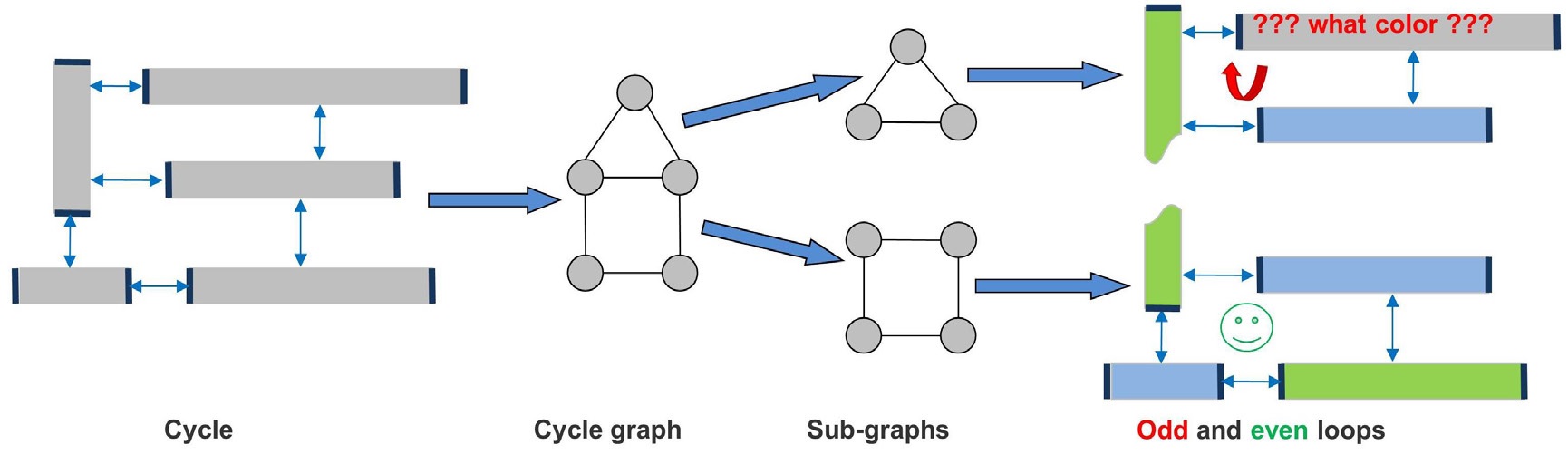

JLPEA | Free Full-Text | Coverage Layout Design Rules and Insertion Utilities for CMP-Related Processes

Chip Variability Mitigation through Continuous Diffusion Enabled by EUV and Self-Aligned Gate Contact | Semantic Scholar

Enzyme-Assisted Microbial Electrosynthesis of Poly(3-hydroxybutyrate) via CO2 Bioreduction by Engineered Ralstonia eutropha | ACS Catalysis

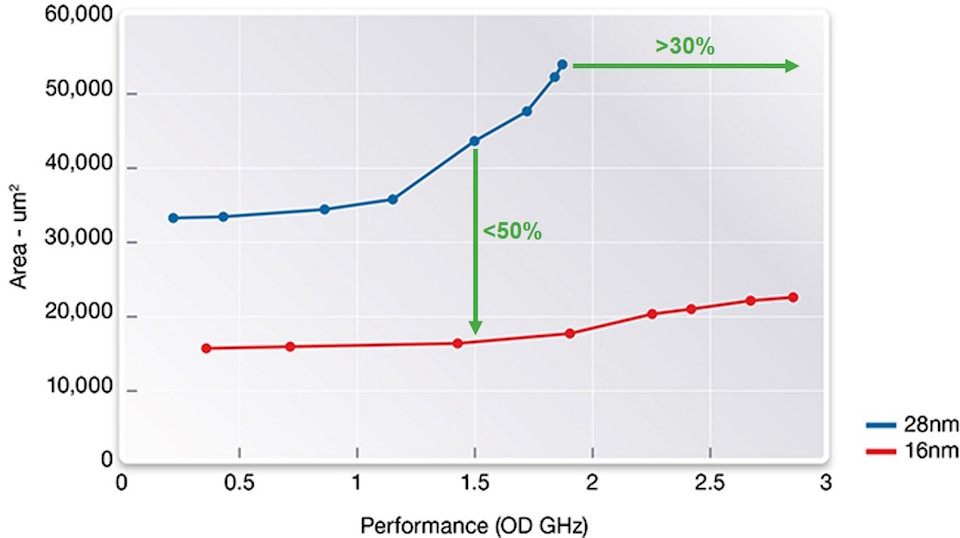

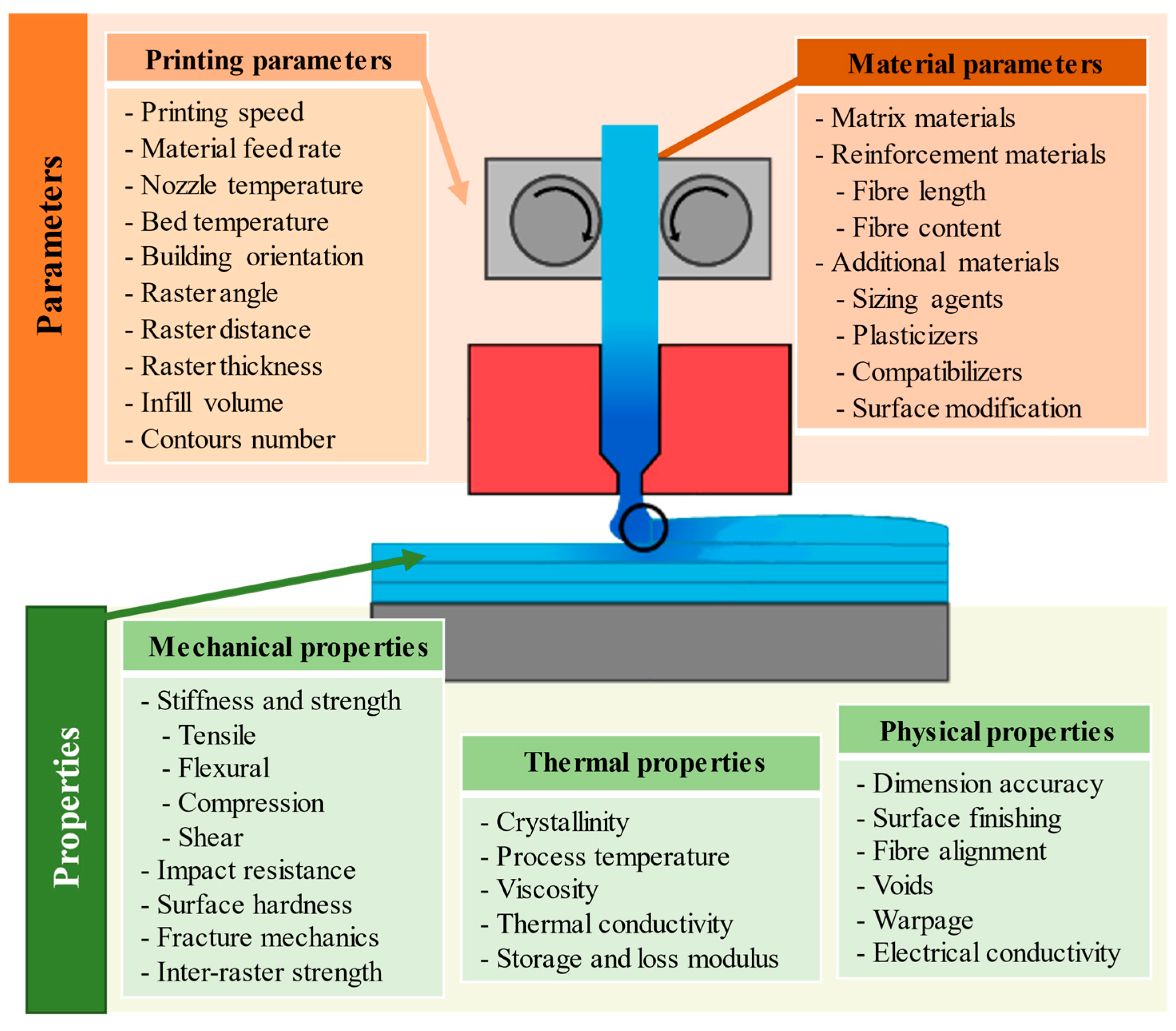

J. Compos. Sci. | Free Full-Text | Fused Deposition Modelling of Fibre Reinforced Polymer Composites: A Parametric Review

Mechanism for Diffusion through Secondary Cell Walls in Lignocellulosic Biomass | The Journal of Physical Chemistry B